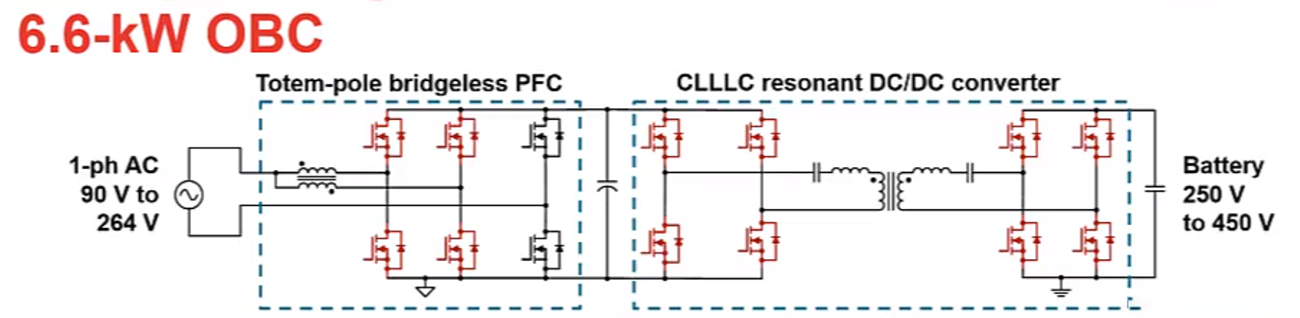

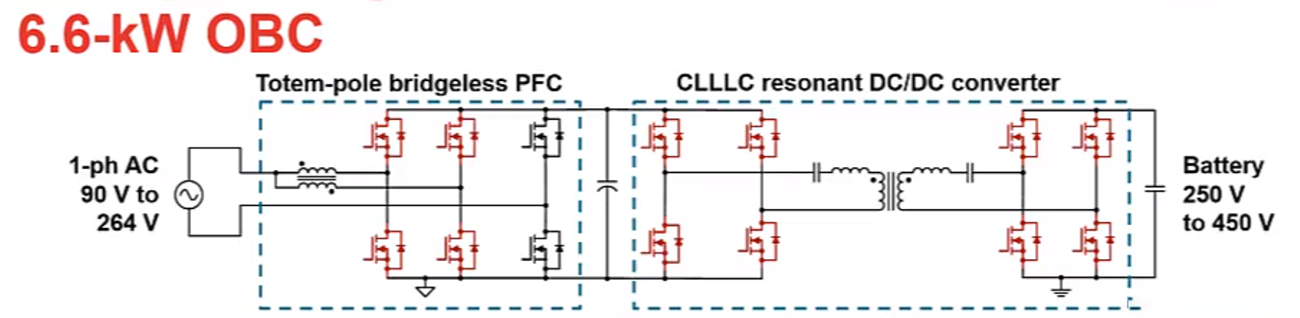

Using a 6.6kW GaNOn-Board Charger (OBC) as an example, let's first address the question: why use GaN for high-performance design? We will achieve this by comparing and contrasting how GaN stacks up against silicon and silicon carbide. From there, we will delve into details about power, layout, thermal management, and control.

Advantages of GaN

GaN technology allows faster switching speeds, minimizing losses and increasing power density. Compared to silicon and silicon carbide, GaN devices exhibit lower losses at high power levels, enabling higher efficiency across a wide load range. This performance is further enhanced in resonant topologies, which benefit significantly from soft switching at high frequencies.

Challenges in GaN Applications

Most circuits using GaN today rely on discrete drivers and transistors. This approach offers the advantage of using standard packages like TO-247. However, it also comes with several drawbacks.

A separate driver means the source connection between the GaN FET and the driver loop can be longer than desired. This length, combined with parasitic inductance in the driver and package leads, results in significantly slower turn-on speeds, additional overshoot, and ringing. These effects contribute to higher losses, which limit how high switching frequencies can be pushed. Ultimately, these losses lead to higher solution costs and larger solution sizes. Integrating the driver with the GaN FET minimizes these effects, reducing solution cost and size. This approach requires a special package but offers the potential for additional features such as integrated overcurrent protection and temperature sensing. The package can also provide top-side cooling for optimal thermal performance.

A dual-phase PFC converter, operating disconnected from the single-phase of the AC mains, follows. This is succeeded by a CLLLC resonant

DC-DC converter tasked with charging the 400V battery system of an electric vehicle, delivering up to 6.6kW of power. The system must deliver full output power from 208V RMS input voltage downward, with maximum output power decreasing linearly below this input voltage.

This design targets a power density of over 60W per cubic inch while maintaining system efficiency above 96%. To stay within thermal limits of all components at a coolant temperature of 65°C, this is necessary. Older designs of this kind typically required two microcontrollers.

Two control schemes were considered for the PFC converter: continuous conduction mode (CCM) and critical conduction mode (CRM). For CCM, peak current is much smaller than in CRM. Consequently, RMS current through the FET is higher in CRM. However, CRM benefits from requiring smaller inductors and offering soft switching when input voltage is less than half of the output voltage. Above this input voltage level, valley switching is achievable, resulting in slightly lower switching losses for the FET compared to pure hard switching.

For our application, the CRM approach requires three phases due to higher peak and RMS currents. Conversely, CCM can operate in two phases. Additionally, CRM PFC requires more complex control schemes, and the variable switching frequency may necessitate more sophisticated EMI filters.

Our power density target exceeds 60W per cubic inch, with required system efficiency above 96%. To achieve this, the PFC converter must exceed 98% efficiency. To meet the power density goal, increasing switching frequency is essential to reduce magnetic component size. However, to achieve the efficiency target, a lower switching frequency is preferable to minimize switching losses in the GaN FETs. Balancing higher switching frequencies and selecting the appropriate number of phases to avoid thermal stress on the GaN FETs is key.

Considering CISPR 32 Class B emission limits, switching frequency impacts EMI spectra multiplied by the number of phases. This means the fundamental harmonic of a two-phase design will appear at twice the switching frequency of a single-phase. EMI constraints are also why CRM-controlled PFC requires more complex filters. Variable switching frequencies can easily enter frequency ranges with stricter limits, especially in high power density designs.

A dual-phase PFC operating at 120kHz was adopted. While three PFC phases improve overall efficiency, they occupy more space and fail to meet the power density target. To further enhance PFC power density, a custom-designed coupled inductor was used. Employing interleaved operation and negative coupling of the inductors allowed ripple current cancellation, significantly reducing the required inductance. Our design achieved approximately 30% volume reduction for the inductor compared to a solution using two independent inductors. The coupling factor of the inductors played a crucial role in the design.

Similar to the PFC, identifying how to maximize efficiency while minimizing size was necessary. Ultimately, we achieved over 98% efficiency, meeting the power density requirement of over 60W per cubic inch. As a reference, efficiencies of the CLLLC converter with and without bias power and some switching waveforms of the converter operating at full load are provided.

This is particularly challenging for resonant converters, as they need to act as both step-down and step-up converters. As output voltage decreases, the required current increases. Below, we discuss several factors crucial to achieving this result, including topology trade-offs, power stage design, thermal management, layout best practices, and control optimization.

To ensure the smallest and most efficient solution possible, two topologies were thoroughly considered: the dual active bridge (DAB) converter and the CLLLC converter. The CLLLC is a variant of the more popular LLC converter.

CLLLC and the dual active bridge are essentially the same topology. Their primary differences lie in how they are controlled and the selection of reactive components.

Each converter highlights two factors. The first is the RMS current through the switches, which accounts for most of the losses in the switches. The second is the converter's ability to maintain zero-voltage switching (ZVS).

CLLLC was chosen because it can maintain ZVS over a wider range of operating conditions while having lower RMS currents. Both factors lead to higher efficiency and easier thermal management.

After selecting the topology, we considered the desired operating frequency for the converter. Frequency is the most significant lever GaN offers to minimize solution size. While GaN FETs are effective for both hard and soft switching at high frequencies, a holistic approach considering the impact of operating frequency on magnetics is crucial.

From a volume perspective, magnetics are typically the largest components in a DC-DC converter. To minimize size, we aim for the highest possible switching frequency.

Firstly, core losses are a function of frequency and flux density. We aim to ensure frequency choices do not result in excessive core losses, surpassing thermal management limits. Secondly, while we aim to minimize operating points that lose ZVS, we also need to control heat generation in GaN switches when ZVS is lost.

Thirdly, as frequency increases, total dead time can occupy a larger portion of the cycle. When this occurs, converter efficiency decreases. Fourthly, higher operating frequencies demand that the processor executes more instructions within shorter time intervals.

For these reasons, resonance frequencies between 500kHz and 1MHz were found to be a good starting point. In this range, magnetic volume reductions were significant. For instance, a transformer optimized for 500kHz occupies only 35% of the volume of one optimized for 100kHz.

A single PIC28x200MHz core can comfortably control PFC and CLLLC operation, providing approximately 170MIPS or million instructions per second at 500kHz. Finally, dead times between 50 and 100ns were considered reasonable.

When making design choices, we considered several factors. For example, flux density and operating frequency influence losses through core loss and field edges. Magnetizing inductor current levels affect efficiency through their ability to maintain ZVS and the resultant RMS current. Turns ratios directly impact currents in the windings and FETs. Operating frequency significantly influences RMS currents and ZVS capability.

Lastly, it is worth mentioning why we chose the CLLLC converter over the CLLC converter. The reason is that CLLLC achieves better performance in discharge mode compared to CLLC. This is due.